# MAX 10 -> The Next Step In Low Cost FPGA Integration

FPGA World September 2015

#### Innovation Leader Across the Board

FPGAs and CPLDs

Low Cost, Non-volatile

**FPGAs**

Cost/Power Balance Mid-range FPGAs

**FPGAs**

SoC & Transceivers SoC & Transceivers

**FPGAs**

Optimized for High Bandwidth **PowerSoCs**

High-efficiency **Power Management**

#### RESOURCES

Embedded Soft and Hard Processors

> Nios° II **ARM**

Design Software

**DSP Builder**

**Development Kits**

Intellectual Property (IP)

- Industrial

- Computing

- Enterprise

# GENERATION Portfolio of FPGAs and SoCs

#### **TSMC 55 nm Embedded Flash**

Instant-on, low-cost, non-volatile FPGAs

#### TSMC 20 nm

**Highest Performance** 20 nm FPGA and SoCs

#### **Intel 14 nm Tri-gate**

2x Higher Core Performance vs. 28 nm

Best in class

Semiconductor

Innovation & Technology

Compelling New Device Architectures

Strategic Investments

That Open

Up New Markets

# **Expanding Opportunities for FPGAs**

2X

Core Performance

5.5 M Logic Elements

Heterogeneous 3D SiP Integration

Intel 14 nm Tri-Gate

Most Comprehensive Security Quad-Core

Cortex-A53

ARM Processor

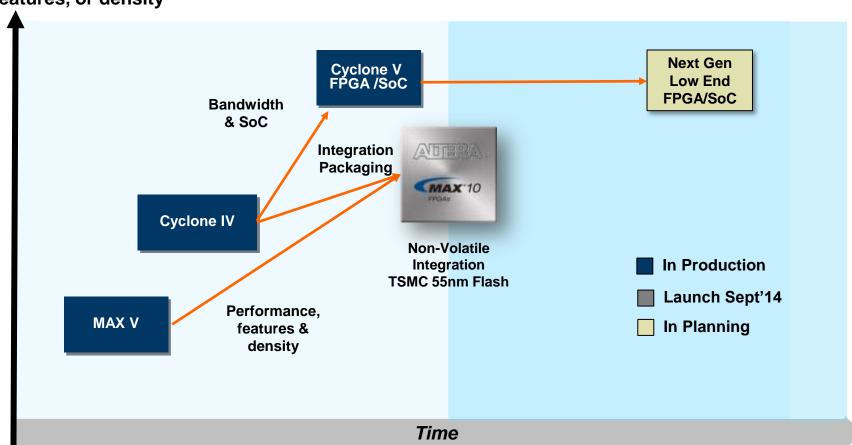

#### Altera Continues Focus & Investment in Low End Families

More performance, features, or density

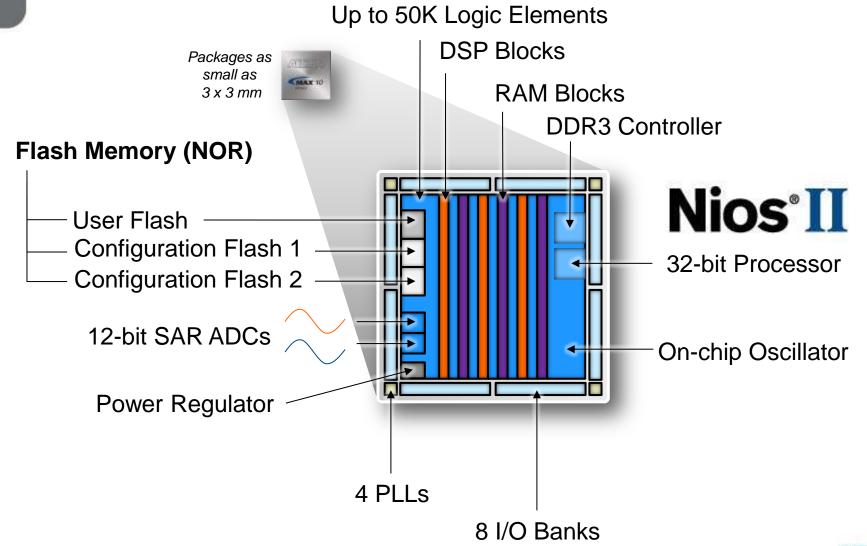

#### What makes it different?

It's time to rethink what an FPGA is.

altera.com/max10

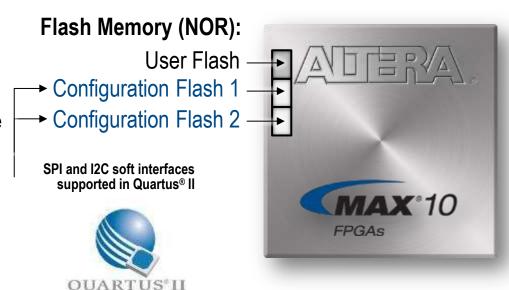

- Dual Non Volatile Images

- Internal Flash to hold two images

- Faster time to operation

- Secure Configuration

- Two stage boot feature, AES

- Integrated ADC

- Flexible sampling

- Soft Processor Support

- Secure Internal Boot

- Single Supply

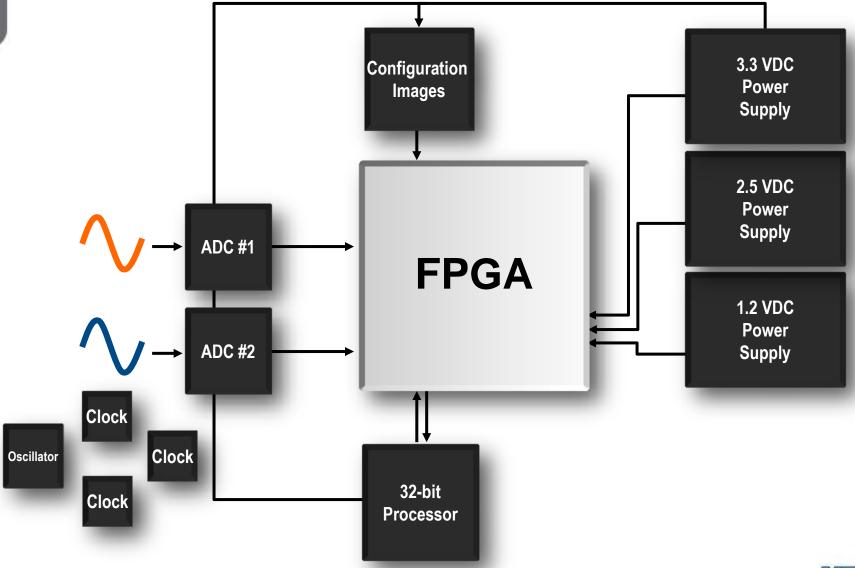

# **Traditional FPGA System Components**

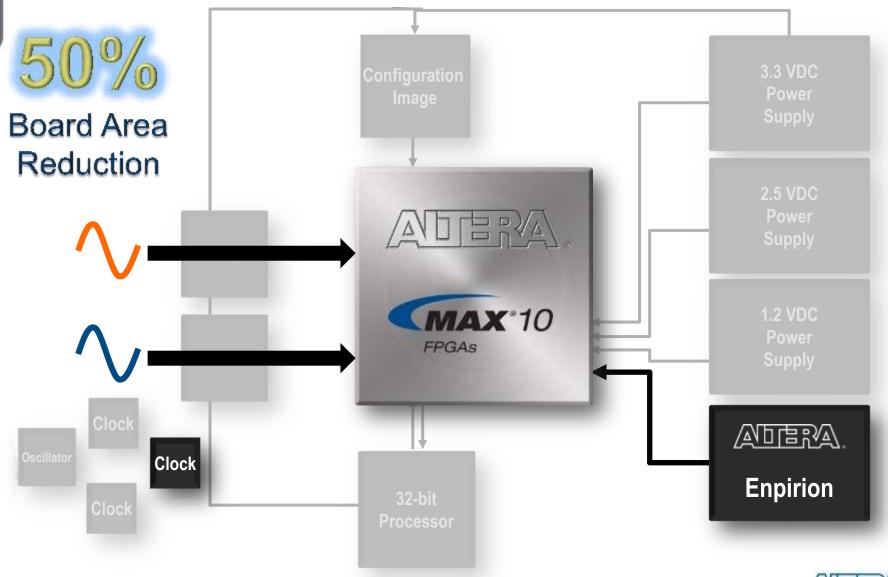

# MAX 10 Simplifies Traditional FPGA Systems

### Lower BOM, Smaller PCB Area, Instant-on Configuration

#### Integrated Embedded Flash Increases System Value

- Lower total cost of ownership

- Reduced BOM

- Smaller board area

- Reduced system risk

- Fewer vendors to manage

- Simpler PCB design

- Supports long life cycles

- Fail-safe remote updates

- Store two configuration images

- Improved system management

- Instant-on configuration

- Power-up sequencing

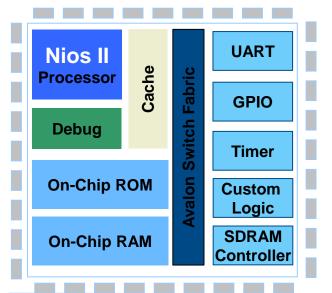

#### Embedded Processing Capabilities Increase System Value

- Single-chip embedded processor system

- Soft core Nios II processor support

- Very small footprint

- No external RAM or storage needed

- User-customizable processor

- Flexibility MCUs don't offer

- Supports real-time applications

- Configuration in under 10 ms

- Meets automotive and industrial regulatory requirements

- Supports longer life cycles

Customizable logic

#### Increase System Value with Integrated Analog Blocks

- In-chip system monitoring

- Integrated ADCs

- Reduce board space

- Flexible sample sequencing

- Lower latency

- Measure environmental conditions

- Integrated temperature sensor

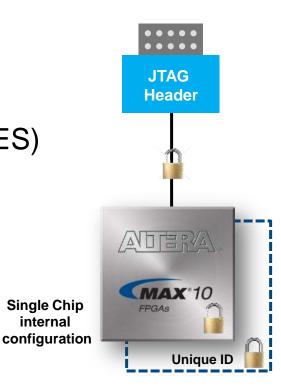

#### Increase Security by adding Anti Tamper Features

- Single chip solution with up to 2 secure images

- Advanced Encryption Standard (128-bit AES) protection

- Non-volatile key for external & internal configuration

- JTAG port security protection

- Read disable or Read/Write disable (OTP)

- Prevents reverse engineering

- Chip ID

- Non volatile 64 bit unique ID for asset traceability

- Verify Protect

- Allows disabling of CFM read back

internal

#### MAX 10 FPGA Customer Benefits

## **Lowers System Cost**

# **Increase Board Reliability**

| Single-chip integration item | Customer Benefits                               |  |  |

|------------------------------|-------------------------------------------------|--|--|

| N components 2 1 component   | Higher system reliability (less failure points) |  |  |

| N-components → 1 component   | Reduced BOM/System Cost                         |  |  |

| Doduced DCD Feetprint        | Simpler PCB Design                              |  |  |

| Reduced PCB Footprint        | Fewer PCB layers → Lower PCB cost               |  |  |

| Fewer Suppliers              | Less vendors to manage                          |  |  |

| PLD have Longer Life-cycles  | Avoids EOL vs. other technologies               |  |  |

#### So where does it fit ?

No right or wrong answer

Consumer

**Motor Driving**

Automotive - Infotainment

Connectivity

**Embedded Vision**

Sensor Fusion

Commercial

Secure Applications

Functional Safety

Motor Control

Industrial – Factory Automation

Machine Vision

#### MAX 10 FPGA – Family Plan

| Device | LEs    | Block<br>Memory<br>(Kbits) | 18x18<br>Mults | PLLs | Internal<br>Config. | User<br>Flash <sup>1</sup><br>(KBytes) | ADC,<br>TSD | External<br>RAM<br>I/F |

|--------|--------|----------------------------|----------------|------|---------------------|----------------------------------------|-------------|------------------------|

| 10M02  | 2,000  | 108                        | 16             | 1, 2 | Single              | 12                                     | -           | Yes <sup>2</sup>       |

| 10M04  | 4,000  | 189                        | 20             | 1, 2 | Dual                | 16 – 156                               | 1, 1        | Yes <sup>2</sup>       |

| 10M08  | 8,000  | 378                        | 24             | 1, 2 | Dual                | 32 – 172                               | 1, 1        | Yes <sup>2</sup>       |

| 10M16  | 16,000 | 549                        | 45             | 1, 4 | Dual                | 32 – 296                               | 1, 1        | Yes <sup>3</sup>       |

| 10M25  | 25,000 | 675                        | 55             | 1, 4 | Dual                | 32 – 400                               | 2, 1        | Yes <sup>3</sup>       |

| 10M40  | 40,000 | 1,260                      | 125            | 1, 4 | Dual                | 64 – 736                               | 2, 1        | Yes <sup>3</sup>       |

| 10M50  | 50,000 | 1,638                      | 144            | 1, 4 | Dual                | 64 – 736                               | 2, 1        | Yes <sup>3</sup>       |

#### Notes:

- 1. User Flash depends upon configuration option.

- 2. SRAM only.

- 3. SDR SDRAM, SRAM, DDR3, DDR2, or LPDDR2.

- 4. ADC blocks available on die but may not be available in low pin count packages.

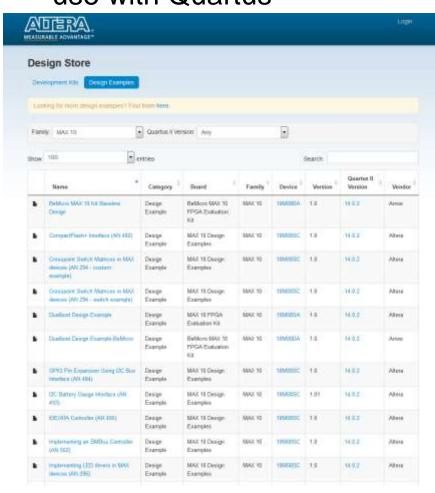

# **Development Tools and Solutions**

## Quartus II Software and IP Support

- Quartus® II software

- Number one design software in performance and productivity

- MAX 10 FPGA compilation & EPE support

- Flash and ADC Megawizards (New!)

- Analog Tool Kits for ADC evaluation and debug (New!)

- Includes Qsys system integration and DSP Builder for increased productivity

- Nios II support and DSP Builder + Advanced Block-set

- Abundant IP & reference designs

- Altera Design Store (New!)

## MAX10 FPGAs App Notes & Design Examples

## Available on Design Store

| AN 496 - Using the Internal Oscillator in Altera MAX Series                   |

|-------------------------------------------------------------------------------|

| AN 547: Putting Altera MAX Series in Hibernation Mode Using User Flash Memory |

| AN 425: Using the Command-Line Jam STAPL Solution for Device Programming      |

| AN 502: Implementing an SMBus Controller in Altera MAX Series                 |

| AN 630: Real-time ISP and ISP Clamp for Altera MAX Series                     |

| AN 494: GPIO Pin Expansion using I2C Bus Interface in Altera MAX Series       |

| AN 485: Serial Peripheral Interface Master in Altera MAX Series               |

| AN 486: SPI to I2C Using Altera MAX Series                                    |

| AN 488 - Stepper Motor Controller using Altera MAX Series                     |

| AN 294: Crosspoint Switch Matrices in Altera MAX Series                       |

| AN 501: Pulse Width Modulations Using Altera MAX Series                       |

| AN 500: NAND Flash Memory Interface with Altera MAX Series                    |

| AN 509: Multiplexing SDIO Devices Using Altera MAX Series                     |

| AN 490: Altera MAX Series as Voltage Level Shifters                           |

| AN 265: Using Altera MAX Series as a Microcontroller I/O Expander             |

| AN 286: Implementing LED Drivers in Altera MAX Series                         |

| AN 498: LED Blink Using Power Sequencing in Altera MAX Series                 |

| AN 495: IDE/ATA Controller Using Altera MAX Series                            |

| AN 492: CF+ Interface using Altera MAX Series                                 |

| AN 493: I2C Battery Gauge Interface using Altera MAX Series                   |

| AN 491: Power Sequence Auto-start Using Altera MAX Series                     |

#### MAX 10 Designs in the Design Store

Long list of MAX 10 designs - tested, packaged, and ready to use with Quartus

|   | Votage Level Stations (AV 200)                                             | Design<br>Example  | MAX 10 Design<br>Exemples                  | 8860.10  | 1MARK     | 10  | 11.02   | Admir   |

|---|----------------------------------------------------------------------------|--------------------|--------------------------------------------|----------|-----------|-----|---------|---------|

|   | Design the Interest Coordinate or NAVI.<br>Revious (WV-PR)                 | Design<br>Energie  | MAX 10 Design<br>Energies                  | MAC 10   | mond      | 1.0 | 14.0.2  | Attera  |

|   | Stagger Milder Controller (Mil 488)                                        | Design<br>Example  | MAX 10 FPGA<br>Enthration N3               | SAUL 10  | VORDOLLA, | 10  | 14.0.2  | Atteria |

| ٠ | The poor foliate Commoline (AN 488)<br>Traditions                          | Design<br>Example  | SMilico MAI 18<br>PPGA Evaluation<br>FOI   | MAK 10   | MINISTER, | 10  | 14.0.2  | Anne    |

|   | Striple PWM Design                                                         | Design<br>Example  | Beldicos MAXI.18<br>PPGA Evaluation<br>KIX | 9007,10  | TOMOSEIA  | 89  | (94.62) | Attex   |

| • | Soul Engrand books Motor<br>(MC48)                                         | Design<br>Example  | MAX 10 Design<br>Exemples                  | 3000 (6) | 10M/890   | X9  | 10.02   | Attors  |

|   | Harrison Fractury Settings LESS<br>Plants                                  | Design<br>Example  | MAX 10 FFGA<br>Evaluation 103              | MALTE    | TEROPSA   | 10  | 14.02   | Attent  |

|   | PANCeugn                                                                   | Design<br>Exercise | MAX 10 FPOA<br>Evenetica Kit               | 864.10   | TOROGO,   | 1.0 | 14.02   | Altre   |

| • | Fusing Atena Max Sense in<br>Historia saling User Plank<br>Memory (AMILET) | Design<br>Example  | MAX 10 Design<br>Examples                  | MAX 10   | VENDER    | 10  | 14.00   | Altera  |

|   | Pulsa Wells Medidation (AN SR1)                                            | Design<br>Example  | MAX 10 Danigs<br>Examples                  | 1001.10  | TOMOSSC   | 1,0 | 10.02   | Attex   |

| ٠ | Power Sequence Auto Start (IVIII<br>4311)                                  | Design<br>Exemple  | MAX to Design<br>Examples                  | 3000 16  | HMARSO    | 1.0 | 14.0.2  | Alberi  |

|   | On the Temperature Service Decays<br>Exemple                               | Deligit<br>Example | MAX 10 FPGA<br>Evaluation His              | MALTE.   | TEMOCSA   | 10  | 11.0.2  | Attent  |

| ٠ | 6000 Flash Monney Imadaca (00)<br>600                                      | Design<br>Everyte  | MAX 10 Design<br>Examples                  | SULE 10  | TOMORIC   | 10  | 14.02   | Atters  |

|   | Multiple only SDIO Devices (HSI<br>100)                                    | Design<br>Example  | MAX 10 Design<br>Examples                  | 664K-10  | VINESC    | 10  | 16.00   | Alleca  |

| ٠ | Murameraties I/O Engander (All<br>250)                                     | Deerge<br>Exemple  | MAX 10 Diorge<br>Exemptes                  | 944(10   | 1014(095) | 1,0 | 14.0.2  | Attes   |

| • | MAZ 18 Estimate 10 Baseline<br>Design                                      | Design<br>Example  | MAX W FPGA<br>Evaluation IO                | MAC III  | MANUSA    | 1.0 | 14.002  | Albera  |

|   | (401.488)                                                                  | Example            | Energies                                   |          |           |     |         |         |

#### Altera MAX 10 Kit Demos / Design Examples

| Kit Demos and Design Examples                  | Available | Target         | Location      |

|------------------------------------------------|-----------|----------------|---------------|

| Sleep Mode Demo Design Dev Kit                 | Now       | 10M50 Dev Kit  | Kit installed |

| Dual Configuration Dev Kit                     | Now       | 10M50 Dev Kit  | Kit installed |

| Remote System Update Dev Kit                   | Now       | 10M50 Dev Kit  | Design Store  |

| Board Management Controller Reference Design   | Q3'15     | 10M50 Dev Kit  | Design Store  |

| Nios II Golden HW Reference Design             | Now       | 10M50 Dev Kit  | Design Store  |

| Nios II NEEK Full Featured Design              | Q3'15     | MAX 10 NEEK    | Design Store  |

| Nios II Ethernet Design                        | Now       | 10M50 Dev Kit  | Design Store  |

| Nios II MCU Replacement Designs                | Now       |                | Design Store  |

| MAX 10 Kit Base Designs (pin assignments)      | Now       | All Kits       | Design Store  |

| Nios II Arduino LCD Design ( <u>Eval Kit</u> ) | Now       | 10M08 Eval Kit | Design Store  |

Base designs great, fast way to start a kit design

# End Market BU Reference Designs

| Demos and Design<br>Examples       | BU Segment                    | Location     | Target Date*  |  |

|------------------------------------|-------------------------------|--------------|---------------|--|

| Industrial Ethernet Multi-protocol | Industrial-<br>Ethernet       | By request   | Q3            |  |

| Drive-on-Chip FOC                  | Industrial –<br>Motor Control | By request   | Q3            |  |

| DC-DC Conversion                   | Industrial<br>-Motor Control  | Design Store | Available Now |  |

| I/O Module Controller              | Industrial –<br>I/O           | By request   | Late Q2       |  |

| Info: MIPI Demo                    | Automotive                    | By request   | Q3            |  |

| Advanced Driver Assist             | Automotive                    | By request   | Q3            |  |

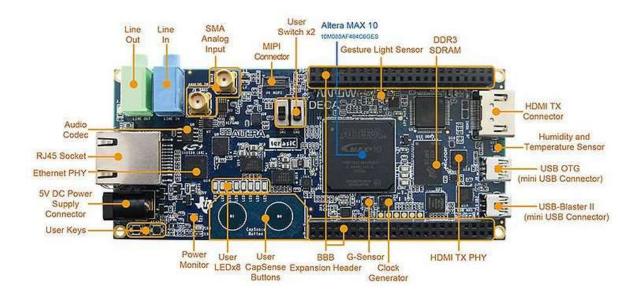

#### MAX® 10 FPGA Kit Portfolio

# MAX 10 FPGA Evaluation Kits

- Ultra Low Cost Eval

- Logic, I/O, power Eval

- Arduino

- 4 package/density options to choose

- Enpirion PowerSoCs

Development Kit

- High Density Development

- Ref Design Platform

- **⋖** 300 MHz DDR3

- ADC Evaluation (SMAs)

- ✓ HDMI TX, HSMC

- Enpirion PowerSoCs

#### Altera NEEK 10 Kit

- CIII NEEK Evolution with applications ported

- Large multi-touch screen

- Sensors, accelerometers, wireless

- Available end of July 2015

#### Arrow DECA 10 Workshops

- Build Hands-On Experience

- Silkeborg, Arrow office, October 6th

- Herley, Arrow office, October 7th

http://www.arroweurope.com/news-events/events-webinars/detail/article/arrow-altera-deca-workshops.html

# Thank You

# It s time to rethink what an FPGA is.

altera.com/max10